chiplets的出現•文章•知識的皮,chiplet設計套件3D IC異質整合|西門子軟件

使用Chiplet Design套件來幫助為3D IC異質整合鋪平道路

幾年後,第一個處理器特別出現在Intel 4004,今天相對簡單. 然後處理器變得更加複雜.

chiplets的出現

在JZD和Discord上進行了討論之後,我告訴自己,寫有關chiplets的文章將對最大的數字有益. 並將書面曲目與JZDS可能發生的事情相反

我沒有寫一張很長的門票,而是寧願文章的格式來獲得更多細節. 我希望能夠教你什麼是chi蟲是什麼,為什麼創建了這項技術以及為什麼它會在未來的幾年中發展.

- 前言

- 魁北克奇普萊特 ?

- 花栗鼠的經濟方面

- 兩個例子:AMD和Intel(Altera)

前言

本文討論了計算機的計算機,電子和建築概念,這些概念可以為某些讀者提供足夠的提升. 我為您提供一些普遍的序言,以更好地了解我們在說什麼.

對於純粹主義者,將做出捷徑,這種普遍化可能能夠包含自願不精確的信息以促進理解.

魁北克奇普萊特 ?

讓我們從最困難的開始,定義什麼是辣椒 !

實際上,奇普萊特一詞出現在1970年代,但近年來它的使用主要是因為那些對複雜處理器或電子芯片感興趣的人(例如FPGA)(可以重新編程其內部邏輯門的芯片). 對於其他人,在房間的底部,您可能從未聽說過這個術語,我們會補救 !

讓我們回到電子芯片的基礎:一塊雕刻矽(著名的晶體管),它被包裹在情況下. 帶有交叉組件,微小的金色或銀線將組件的腿連接到矽. 一開始,芯片由刻有相當粗糙的分辨率(與今天相比)的晶體管組成,功能非常基本:邏輯門,操作放大器等。. 但是,在微型化方面已經取得了巨大進展 !

那時,組件有交叉的腿,有必要將矽芯片連接到這些腿. 它是用薄的銀或金子製成.

幾年後,第一個處理器特別出現在Intel 4004,今天相對簡單. 然後處理器變得更加複雜.

從1970年代開始,IBM開發了MCM組件(多chodu)在單個情況下包括幾芯. 但是這項技術將主要在90年代後期發展. 我們可以注意到1995年發行的英特爾奔馳Pro. 該處理器包括兩個矽芯片:一個嚴格說話的處理器,另一個用於L2緩存內存(處理器和RAM之間的緩衝存儲器,速度更快,但昂貴得多,因為使用處理器).

正如我們在照片中看到的那樣,這兩個芯片的尺寸大致相同,英特爾提供了幾種尺寸的高速緩存L2. 分離緩存內存處理器的優點是能夠通過在情況下放置不同尺寸的芯片來節省處理器芯片的比例。.

即使IBM繼續開發MCM組件,這種類型的組件仍然相對欠發達. 注意2004年發布的IBM的Power5. 跳蚤的互連是在外殼內完成的.

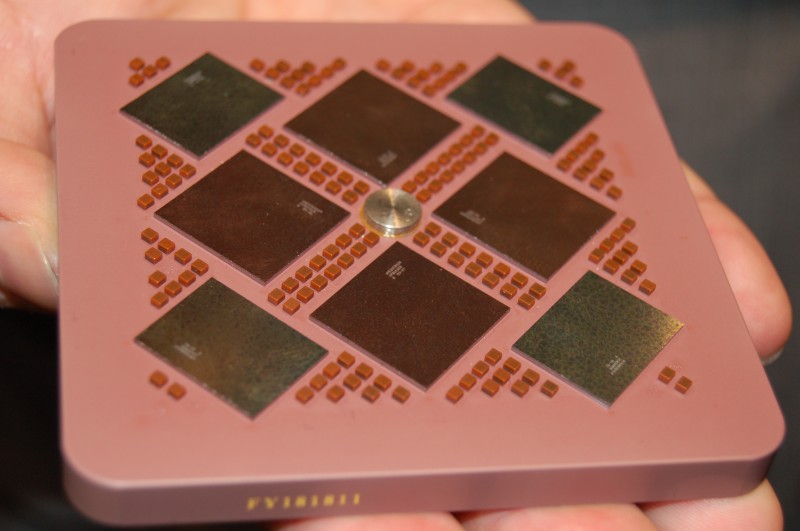

如今,該技術已經進化,MCM芯片已經存在於帶有AMD處理器的消費產品中. 在這裡,我們可以看到一個EPYC 7702處理器(2019年8月發布),該處理器由9個互連的矽芯片組成:8個包含內核和緩存內存的芯片以及連接其他8的中央芯片,並管理DDR以及信號D’入口/入口/退出(SATA,PCI Express,USB,等.)).

但是告訴我jamy,什麼是chiplet ?

啊,是的,我得出了一點

實際上,芯片是MCM中存在的矽芯片之一. 使芯片與其他芯片互連. 是的,這相對簡單,但是您必須顯示一些漂亮的照片才能理解

然而,要對芯片的含義更加精確,這個想法不一定是將幾個不同的芯片鏈接在一起. 還有一個通用芯片的概念,可以重複使用,而不是專用於特定的處理器參考.

花栗鼠的經濟方面

在介紹圖像之後,讓我們現在理解為什麼芯片將來會發展. 為此,有必要返回製造電子跳蚤的過程.

舒適地坐在扶手椅上,因為從沙灘旅行會很長

不,等等 !

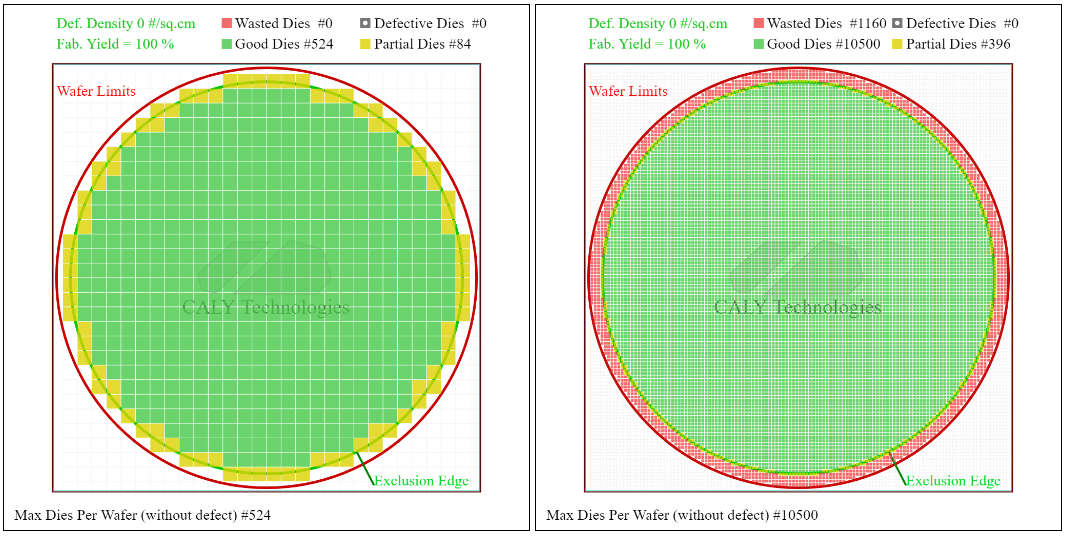

我們將花費矽製造的整個部分. 我們會讓我們感興趣的是跳蚤的分佈(死)在矽蛋糕上(晶圓),尤其是隨著雕刻雕刻的增加而產量的發展.

但是在產量的這一方面,我們必須談論死亡的最大物理大小. 實際上,在矽煎餅上,芯片的相同設計重複了幾次(數十甚至一百次). 這種設計的印像是通過紫外線光學完成的. 但是,有一組鏡頭和光學機制,可以防止在整個矽蛋糕上雕刻一個模具.

我們對跳蚤的複雜性越複雜,我們想將晶體管放置得越多,因此我們必須增加芯片的尺寸,或者增加雕刻的美味以適合在同一表面上的更多晶體管. 但是感覺到還有其他限制和限制.

這就是為什麼Chiplet原理繞過這些限制很有趣的原因:使用幾個小矽芯片連接在一起,使芯片更複雜,但無法以整體構造的方式雕刻.

現在回到產量(屈服 用英語講). 首先,晶圓的形狀是圓形的,我們想用矩形芯片雕刻它. 整個矽不使用. 但是邊緣的死亡越小,我們就越能擁有整個模具. 這與視頻遊戲中的混音是相同的原理:形成圓形的像素越小,我們意識到刻痕的次數就越少。.

在上面的示例中,如果我們報告部分死亡的模具總數(良好和偏見),我們將獲得13.在5×5 mm和3的死亡情況下為8%.在1×1 mm死亡的情況下為6%. 模具越小,邊緣上的模具越有效,這會增加產量.

您還可以在晶圓的中心製成大型模糊,並在邊緣使用較小的模具以優化因混疊而產生的收益率.

說Jamy,為什麼我們要使用圓形晶狀體製作矩形跳蚤 ?

好吧,這是因為製造矽的方法稱為Czochralski工藝,該過程以圓柱體的形式提供矽,切成非常細的切片以提供 晶片.

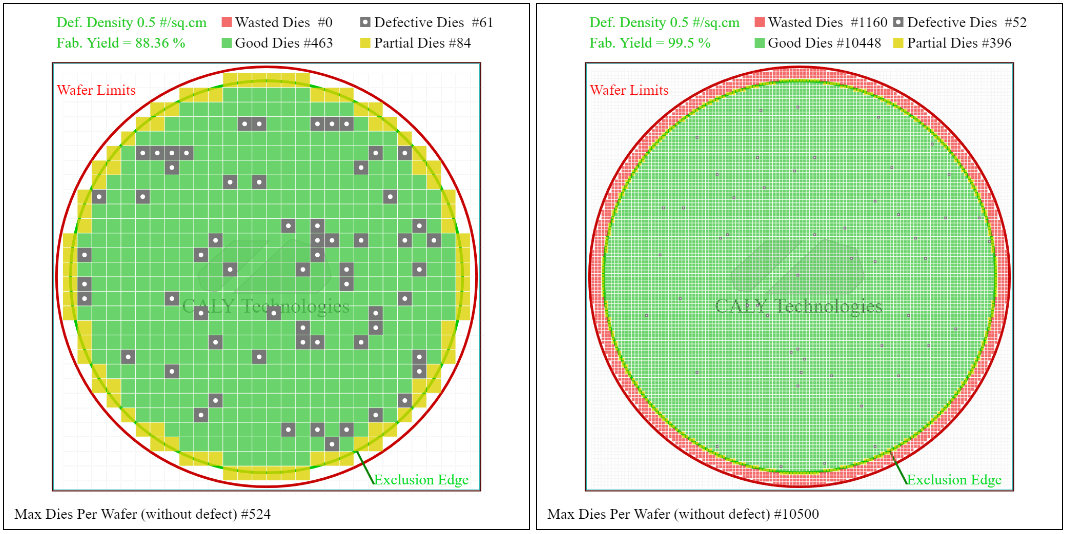

其次,產量受到晶圓上可能出現的缺陷的影響. 您可以想到落在晶圓上的灰塵顆粒.

我通過添加0的故障密度恢復了上一個示例.每cm²5. 現在比較 產量製造 對應於功能模具數量與生產的產品總數之間的比率. 在5×5毫米死亡的情況下,產量為88.4%,而1×1毫米死亡,產量為99.5%.

因此,擁有少量模具以優化電子跳蚤的生產是雙重有趣的. 然而,將復雜的芯片切成幾個較小的芯片需要在它們之間傳達這些不同的芯片,因此,我們必須添加來佔用額外空間並使用額外能量的溝通元素.

此外,使用chiplet可以根據功能使用不同的雕刻模具,從而可以通過性能調節最終芯片的成本.

最後,要看的另一個經濟方面是開發新功能的複雜性. 這傾向於擁有準備使用的知識產權塊(功能)的專業公司(或至少在一開始). 例如,處理器製造商將能夠專注於處理器本身的開發,同時購買諸如PCI Express,USB或DDR控制器等功能的模具.

為了促進來自不同製造商的chiplets的互操作性,英特爾,AMD,ARM,Qualcomm,Samsung或TSMC等主要參與者已經在Chipplets,Ucie之間建立了通信標準(UCIE(UCIE)(通用chiplet互連快遞)).

兩個例子:AMD和Intel(Altera)

AMD EPYC

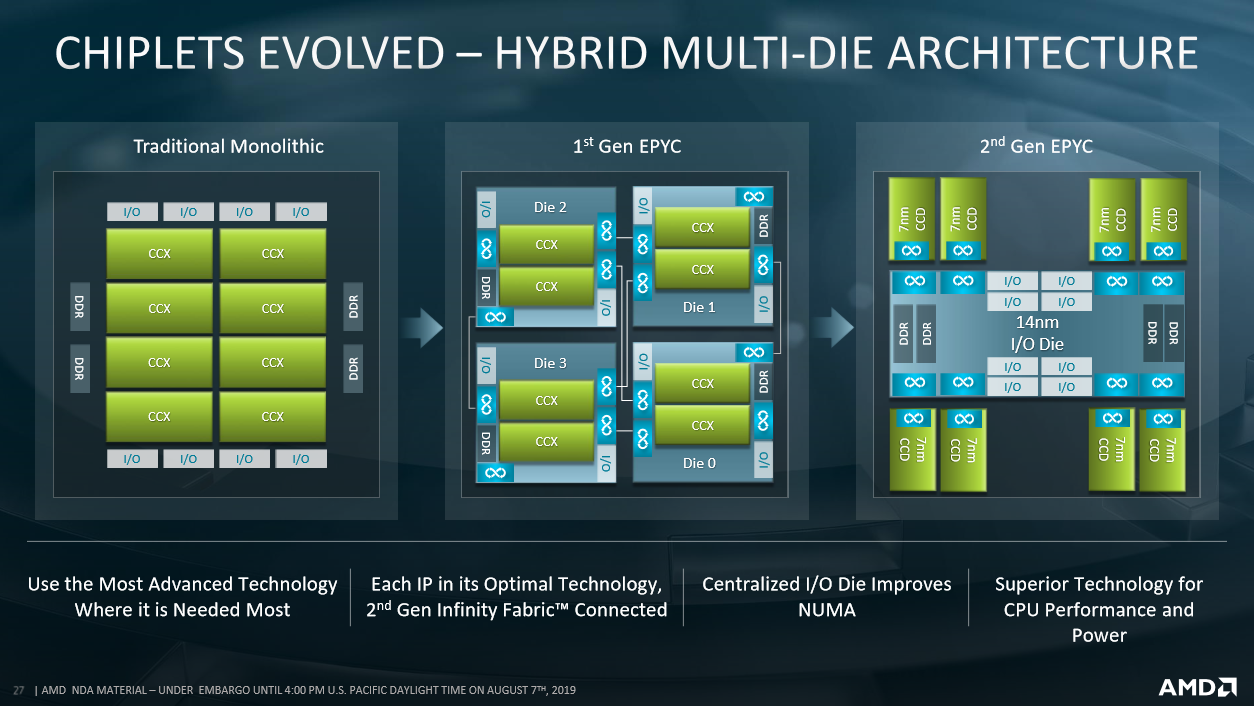

如今,越來越多的處理器使用此芯片技術. 自第一代EPYC處理器以來,AMD使用芯片無限面料.

第一代EPYC處理器看到了一組模具,這些模具可以與完整的處理器等同於無限面料 構成最終處理器. 因此.

這些死亡,或者更確切地說是chiplets 核心計算複合物 (CCX,一組具有緩存內存的內核)以及DDR控制器,管理輸入/輸出(例如PCI Express),並具有用於該的通信模塊無限面料.

小小的微妙之處,第一代EPYC上總是有四個chiplets. 要改變心臟的數量,AMD會停用CCX內的心臟. 例如,具有24個核心,CCX只有3個活性核

因此,第一代使用chiplet的原理作為一種模具的副本/膠合,而不是開發大型整體模具.

對於第二代,AMD將該概念進一步推動. 實際上,CCX現在是獨立的,成對分組 核心計算模具 (CCD)連接 無限面料 管理DDR和稱為條目/出口的模具 我死了 (iod).

AMD完全利用了與功能的分離增加. 確實,CCD刻在7 nm中,而iOD刻在14 nm中.

在AMD呈現下,總結了EPYC處理器芯片中的通過.

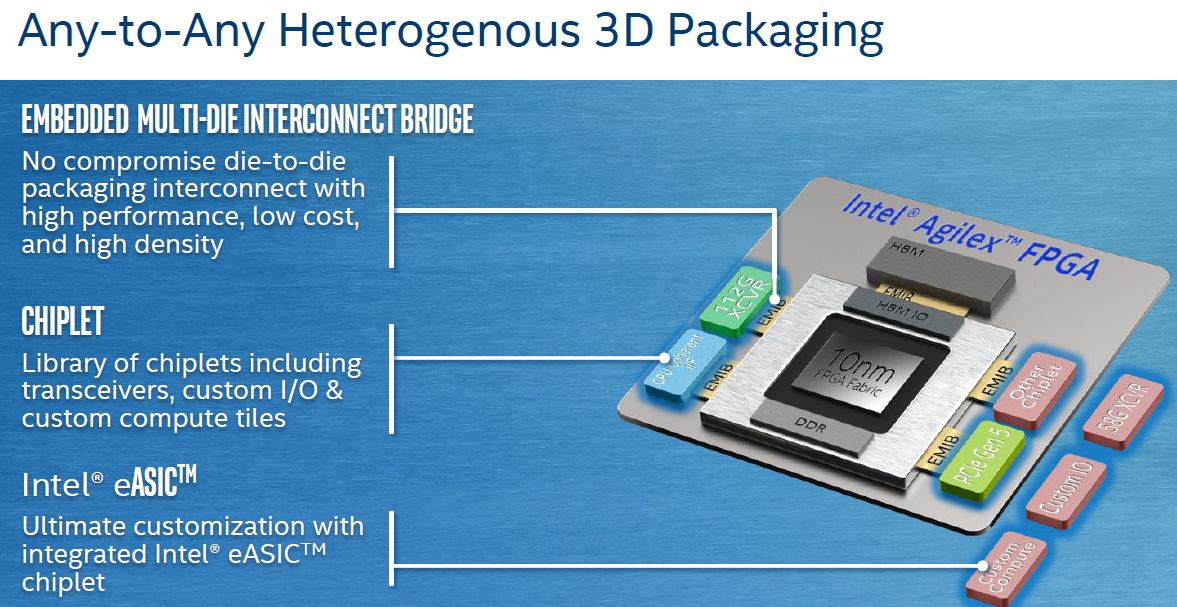

英特爾FPGA(Altera)

英特爾處理器總是單一的芯片,除了我們在本文開頭看到的一些例外. 然而.

這些chiplet主要涉及所使用的thrcense類型(快速鏈接),稱為 瓷磚. 如果英特爾提供這些瓷磚的預定範圍,則必須有可能有自定義的芯片來滿足您自己的需求.

瓷磚除以收發器的最大速度和支持的協議(以太網,PCI Express等。.):p為16克,h為28克,r為32克,等。.

英特爾還喚起了未來的可能性. 目前,公司已經發布了ADC/DAC(JARIETT Technologies)Chiplet以及另一個光學連接(Ayar Labs).

最後,我們不能相信芯片 整體 是死的. 它們始終具有優勢,尤其是在內部交流和延遲方面,這對於需要大型芯片的某些應用程序至關重要.

這是Broadcom及其開關400G芯片的情況.Youtube.com/watch?v = b-cogmbaug4

我希望這篇文章對您有更多的信息,並允許您更多地了解當前芯片的製造. 我試圖普及一個複雜的主題,也希望我能夠在第一段之後留下來

如果某些要點仍然對您來說仍然是神秘的,請隨時發表評論,我將嘗試提供詳細信息.

6條評論

這個答案很有用

很棒的文章,謝謝 @ zeql !

“把我扔給狼,我將退還背包.“ – 塞內卡

這個答案很有用

我想知道chiplets的出現能夠考慮硬件的某種演變(以及 消費者級 那 服務器級)將來,甚至對我們高度設計的整體設計方式進行範式轉變.

某些良好集成的系統(尤其是在蘋果公司)並不僅基於非常有效的“經典” CPU,而是基於幾個專業的輔助芯片,這些芯片可以卸載通才CPU. 在有限的系統作為智能手機中,我們可以找到H265轉碼芯片,AI的計算單元(蘋果神經發動機)當然還有經典的圖形單元.

因此,我佔據了第二代AMD EPYC的圖,我想知道chiplets是否會從完整單元中生產出商業和工業可行的簡單方法,這些單元登上了幾個專用芯片,以在某些任務上實現最佳性能. 例如,一個單元可以提供經典的CCD,但也可以提供DSP,GPU,Transco H265/av1/vp9/…,一個要做AES的芯片,等等。. 並通過iod/infinity製造將其連接. 因此.

它使我想起了APU的概念,但我不知道是否有報告.

這個答案很有用

我想知道chiplets的出現能夠考慮硬件的某種演變(以及 消費者級 那 服務器級)將來,甚至對我們高度設計的整體設計方式進行範式轉變.

某些良好集成的系統(尤其是在蘋果公司)並不僅基於非常有效的“經典” CPU,而是基於幾個專業的輔助芯片,這些芯片可以卸載通才CPU. 在有限的系統作為智能手機中,我們可以找到H265轉碼芯片,AI的計算單元(蘋果神經發動機)當然還有經典的圖形單元.

因此,我佔據了第二代AMD EPYC的圖,我想知道chiplets是否會從完整單元中生產出商業和工業可行的簡單方法,這些單元登上了幾個專用芯片,以在某些任務上實現最佳性能. 例如,一個單元可以提供經典的CCD,但也可以提供DSP,GPU,Transco H265/av1/vp9/…,一個要做AES的芯片,等等。. 並通過iod/infinity製造將其連接. 因此.

它使我想起了APU的概念,但我不知道是否有報告.

因此,您應該知道,芯片通常是使用IP(知識產權)完成的:在“晶體管”級別上銷售的功能已經準備好,但必須將其集成到其設計中.

一個經典的示例是ddr3控制器On -board MicroController. 微控制器的製造商不一定掌握DDR3,並且沒有技能,時間(願望)都不是創建DDR3控制器. 因此,他從控制器中購買IP並將他整合到他的設計中.

您必須成功地看到IP和chiplet的可能性之間的區別. 對我來說,chiplet可以帶來一個或多個高級功能,並且已經通過了雕刻的測試,因此在設計中又一個步驟. 但是仍然存在所有用所有粉刺測試整個土壤的問題. 因此,我們無法創建數百種變體,例如樂高. 它需要最少的經濟現實.

但是,是的,對於一定卷,我們可以創建點菜插座.

最大的優勢是在芯片的生產方面:如果可以拒絕不同的雕刻技巧,那麼在其他零件芯片可以始終以其初始技巧(如果足夠的話)中刻有能夠始終刻有刻板的chiplet。通過較小的雕刻來改進.

這個答案很有用

此外,我認為芯片可以在模塊化設計中使用. 您使用4芯片進行設計,帶有故障的跳蚤在整個生產中分佈,而在4個籌碼上使用4芯片的跳蚤將比有4個工作的籌碼範圍低於下方的範圍,並且便宜一點。.

這簡化了與常規操作有關的設計和工業化.

自由軟件和GNU/Linux Fedora發行的戀人. #Jesuisarius

這個答案很有用

謝謝你這篇有趣的巨型文章. 我會愛你太多的時間來詳細說明您在教程中沒有解釋的每個觀點,以真正理解事物,但無論如何還是有趣的 .

使用Chiplet Design套件來幫助為3D IC異質整合鋪平道路

chiplet是一個特定設計和優化的ASIC模具. 異質綜合(HI)涉及多個多個模具或芯片中的系統包裝(sip)chipplets. 這些設備提供了可觀的好處,包括性能,力量,區域,成本和TTM.

chiplet設計交換(CDX)由EDA供應商,chiplet組成

提供者/彙編商和SIP集成商是一個開放的工作組. 本網絡研討會總結了Chiplet設計套件(CDK)提供的幫助標準化2.5D和3.D IC設計以創建開放的生態系統.

建立成功的生態系統2.5D和3D芯片模型集成

與SOC過程類似,您需要一個用於奇普的生態系統. 關鍵啟用了一般市場採用和基於chiplet設計的部署:包括:

- 技術:2.5 d插入和3D堆疊的模具製造和組裝過程

- IP:標準化的花栗鼠型號

- 工作流:EDA設計流和PDK,CDK,DRM和組裝規則

- 商業模式:chiplet市場

CDX的初始焦點為2.5D基於3D的基於3D的芯片模型遵循. 在網絡研討會中了解有關這些努力的更多信息.

Chiplet Design Exchange(CDX)由EDA供應商,chiplet提供商/彙編商和SIP集成商組成,並且是一個開放的工作組,可以推薦標準化的chiplet模型和工作流程,以促進chiplet生態系統. 本網絡研討會總結了Chiplet設計套件(CDK)提供的幫助標準化2.5D和3.D IC設計以創建開放的生態系統.

建立成功的生態系統2.5D和3D芯片模型集成

與SOC過程類似,您需要一個用於奇普的生態系統. 關鍵啟用了一般市場採用和基於chiplet設計的部署:包括:

- 技術:2.5 d插入和3D堆疊的模具製造和組裝過程

- IP:標準化的花栗鼠型號

- 工作流:EDA設計流和PDK,CDK,DRM和組裝規則

- 商業模式:chiplet市場

CDX的初始焦點為2.5D基於3D的基於3D的芯片模型遵循. 在網絡研討會中了解有關這些努力的更多信息.

洩漏的圖像揭示了GPU AMD Radeon的chiplet雄心勃勃的設計

洩漏的圖像揭示了GPU AMD Radeon的chiplet雄心勃勃的設計

- 經過

- 在新聞中

- 2023年8月16日

洩漏的圖像浮出水面,揭示了帶有Radeon Chiplets的GPU設計. 單個GPU上的13至20種不同的chiplet的設計,證明了雄心勃勃的AMD方法. 這種更複雜的chiplet設計與當前在Rade rx 7900 XTX中使用的NAVI 31矽不同. 儘管GPU的先前迭代被認為是第一代,但它沒有像最近的AMD的Ryzen處理器那樣使用真實的chiplet設計. 但是,NAVI 4C的概念披露代表了一個重大進步,因為它包含了單個基材上的幾個計算芯片以及不同的I/O chiplets. 洩漏的圖像呈現13個chiplets,圖像上未顯示其他內存控制器芯片.

為了確認圖像的真實性,突出了2021年的相關專利,討論並行處理器中的模塊化概念. 專利模式與洩漏的圖像中顯示的設計非常相似,甚至表明在橫杯另一側有更多的chiplets.

不幸的是,已取消了洩漏圖像中介紹的GPU的設計. 這與最近的關係一致,表明AMD的下一代GPU的口音將在Navi 43和Navi 44單片芯片上,而不是用於公眾,而不是在高端組件上. 但是,據推測,AMD將其努力重定向為開發GPU,該GPU由幾個計算芯片組成,用於其未來圖形卡範圍的高端段,可能使用RDNA 5.

儘管實現了遊戲圖形的幾個計算芯片比傳統CPU計算更為複雜,但AMD決定現在克服設計障礙,並為rdna 5的更好解決方案努力被視為一個積極的步驟. AMD制定救援計劃將是有利的,例如改進版本的NAVI 31的新節點.